RISC-V Extension Eliminates Division

RISC-V International, the governing body of the open-standard instruction set, recently approved four new specifications that address multiplication, bootloaders, and debugging, reducing the gap with Arm.

Joseph Byrne

RISC-V International, the governing body of the open-standard instruction set, recently approved four new specifications. Underscoring the fact that defining a microprocessor architecture requires more than defining an instruction set, only one new spec deals with instructions and only one affects hardware design.

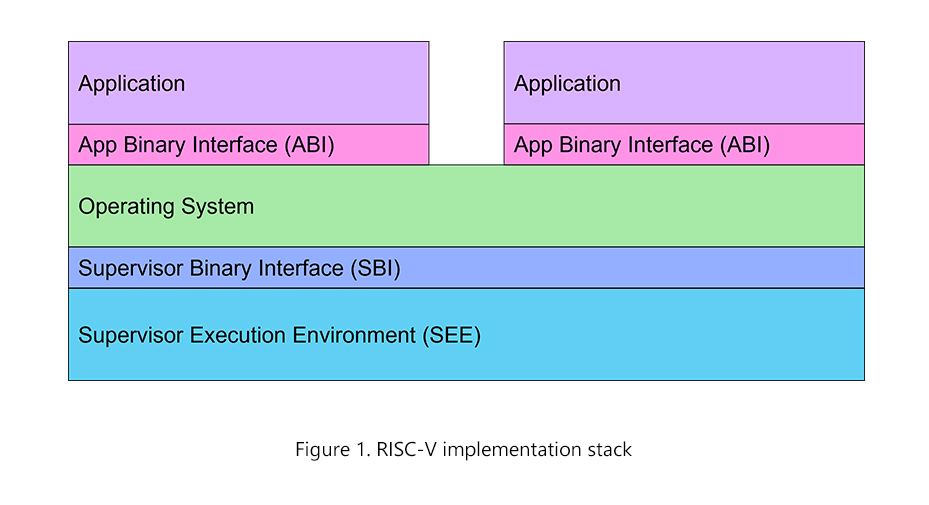

The new Zmmul extension is a subset of the M extension, but it includes just multiplication instructions. The E-Trace specification documents how RISC-V hardware can trace program flow to assist with debugging. The UEFI protocols help the ISA work with that boot-firmware standard, and the SBI revision updates the common layer that OSs can employ for compatibility among RISC-V implementations.

Targeting everything from microcontrollers to server processors, RISC-V is modular. Implementers choose a 32-, 64-, or 128-bit base architecture and add standard or proprietary extensions for their application. The standard modules come from developers who contribute intellectual property and define the ISA under the auspices of RISC-V International. Members include companies that create RISC-V processors, vendors that use RISC-V CPUs in their designs, software developers, universities, and more. RISC-V blends the communal bazaar of free open-source software (FOSS) with formal governance.

Free Newsletter

Get the latest analysis of new developments in semiconductor market and research analysis.

Subscribers can view the full article in the TechInsights Platform.

You must be a subscriber to access the Manufacturing Analysis reports & services.

If you are not a subscriber, you should be! Enter your email below to contact us about access.