Posted: November 9, 2017

Intel/Micron 64L 3D NAND Analysis

The Intel 545S SSD, introduced in June 2017, was the first product to include the Intel/Micron 64L 3D NAND, and one of the first SSD to use 64L. The device boasts a more compacted die floorplan, improved memory peripheral design, and a 90% increase in memory density from 32L.

There are many reasons this device caught our attention, and we have conducted a great deal of analysis on it. We are offering several different types of reports about the Intel/Micron 64L 3D NAND, as well as information available through our various subscription products and tools.

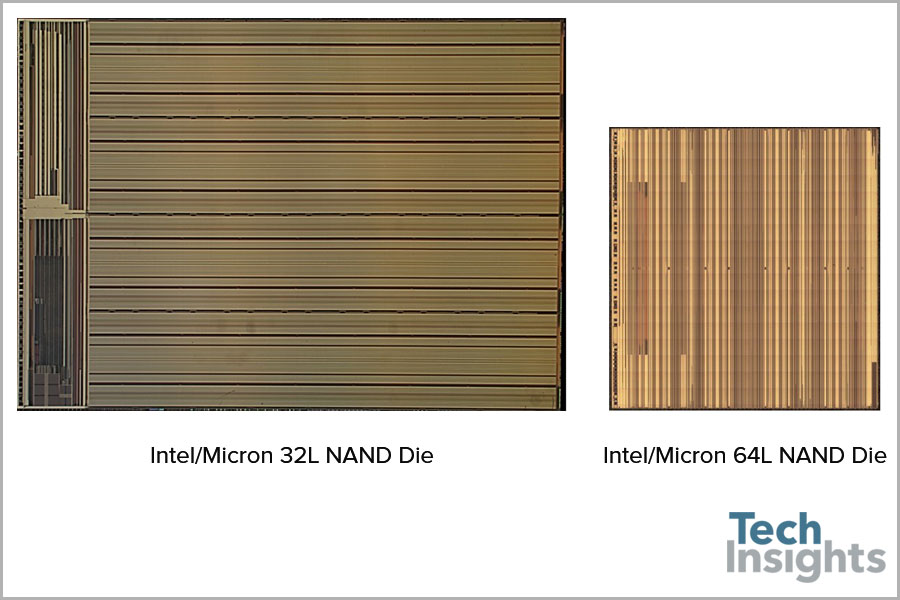

Comparison 32L vs. 64L

Technology Innovations on Intel/Micron 64L FG NAND Flash Device: Comparison 32L vs. 64L

Dr. Jeongdong Choe, Senior Technical Fellow at TechInsights, notes the following comparisons between 32L 3D NAND and 64L 3D NAND.

TechInsights has been analyzing recently-released 64L 3D FG NAND devices from Intel/Micron, and we have found some innovations they successfully developed and applied to 64L NAND products which are quite different from their previous 32L 3D NAND products.

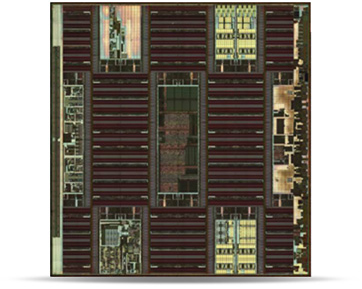

1. Die Size, Memory Density and Array Efficiency: Intel/Micron 64L 3D NAND die (58.18 mm2) size is a quarter of the previous 32L (168.2 mm2). Due to the smaller die size, memory density per die increased from 2.28 Gb/mm2 to 4.40 Gb/mm2, which is an almost 90% increase over their previous 32L 3D NAND products. Die size is 65% smaller than the 32L NAND. Memory array efficiency is 89.8 %, compared to 84.9% in the 32L.

2. Patterning Technology: 64L 3D NAND products use 20 nm technology node (BL half pitch) with a sidewall spacer process such as SADP (Self Align Double Patterning). Previous 32L 3D NAND used 80 nm BL pitch with single Photolithography.

3. Double Stacked NAND String: The 64L 3D NAND string consists of two 32L NAND string stacks, which means 32L + 32L. Intel/Micron developed and mass produced double-stacked NAND string technology for the first time, while other NAND players such as Samsung, Toshiba and Western Digital still use a single NAND string for their 64L 3D NAND products.

4. Memory Tiles: Memory tiles are used but the tile layouts are quite different from Intel/Micron’s 32L NAND dies. There are 32 memory tiles, which means a memory density of 8 Gb/tile. Single tile size on 64L die is 1.10 mm2, while 32L die has 9.14 mm2 tile size. Memory density for each tile reached 7.27 Gb/mm2.

5. Cell Gates: Intel/Micron still use a thin FG (floating gate) with GAA (gate all around) and ONO barrier layers. The total number of gates vertically stacked is 76, where it is likely that two select gates (SGS, SGD) and ten dummy wordlines are placed with 64 active wordlines. In comparison, forty gates were used for the Intel/Micron 32L 3D FG NAND cell structure.

6. Others: Intel/Miron keep CuA (CMOS under Array) which is the same architecture in 32L NAND. The die floor plan looks more compacted, with improved memory peripheral design, including WL driver and page buffer. Mask design and process integration on wordline pad connection are improved as well.

| Items | Intel (32L) | Intel (64L) |

|---|---|---|

| Die Markings | Intel L06B 2014 (M) (C) | Intel B16A 2016 (M( (C) |

| Die Area | 168.2 mm2 (15.36 mm x 10.95 mm) |

58.18 mm2 (7.43 mm x 7.83 mm) |

| Memory Density (/die) | 2.28 Gb/mm2 | 4.40 Gb/mm2 |

| Memory Array Efficiency | 84.9 % | 89.8 % |

| Number of Tiles | 32 Memory Tiles | 32 Memory Tiles |

| Memory (/tile) | 12 Gb / Tile | 8 Gb / Tile |

| Tile Area | 9.14 mm2 (2.75 mm x 3.32 mm) |

1.10 mm2 (1.10 mm x 1.00 mm) |

| Memory Density (/tile) | 1.31 Gb/mm2 | 7.27 Gb/mm2 |

Table 1: Comparison Intel/Micron 32L and 64L 3D NAND Memory Density and Efficiency

Find content like this and more in the TechInsights Platform. Sign-up for free today.