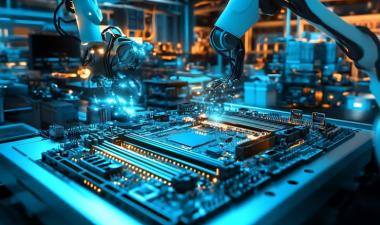

Intel Lunar Lake 16th Gen TSMC N3 Digital Floorplan Analysis

Discover the floorplan analysis of the Intel Core Ultra 7 258V (Lunar Lake) package (SRPMN) including node identification, die utilization, manufacturing costs, and more in-depth examinations.

The Intel Core Ultra 7 258V (Lunar Lake) package (SRPMN) was removed from a MSI Prestige 14 AI+ Evo laptop. The Intel SRPMN_die processor chiplet was fabricated on 300-mm wafers by TSMC, using 3 nm (N3) FinFET high-k metal gate (HKMG) CMOS process, The back-end of line (BEOL) features a total of 20 metal interconnection layers. This die features a quad-core high performance Live Cove CPU, a quad-core high-efficiency Skymont CPU, and 64 Xe GPUs. This analysis includes node identification, BELO stack, bit cell usage, critical dimensions, and digital blocks layout with die utilization calculations for total area for logic, I/O memory, and analog components separately. Manufacturing cost is also provided.